How Could Each Of The Two Proposed Changes Decrease The Size Of An Mips Assemply Program

(Solved) : Assume Would Like Expand Mips Register File 128 Registers Expand Education Gear up Contain F Q26491376 . . .

$9.00

2.sixteen:

![3. [8 points] [Based on 2.16 from the textbook] Assume that we would like to expand the RISC-V register file to 128 registers. (a) How would this affect the size of each of the bit fields in the R-type instructions? b) How would this affect the size of each of the bit fields in the I-type instructions? c) How could this change decrease the size of a RISC-V assembly program? On the other hand, how might this proposed change increase the size of a RISC-V assembly language program?](https://d2vlcm61l7u1fs.cloudfront.net/media%2Ff59%2Ff5949b73-8945-4e01-a75c-31dd1e3aa483%2FphpOUkgi6.png)

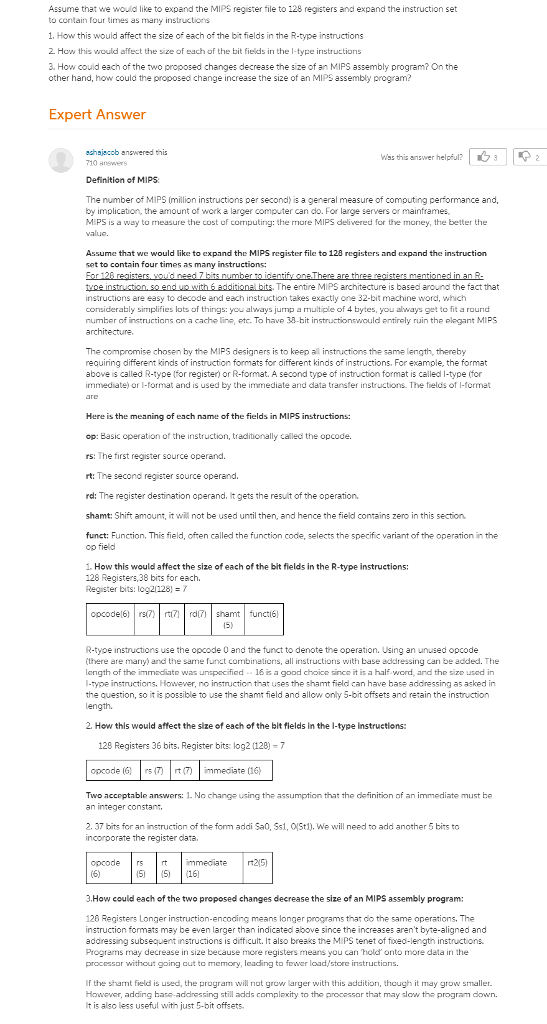

Presume that we would like to aggrandize the MIPS annals file to 128 registers and expand the instruction set up to contain four times every bit many instructions one. How this would affect the size of each of the flake fields in the R-type instructions How this would bear on the size of each of the bit fields in the I-blazon instructions 3. How could each of the ii proposed changes decrease the size of an MIPS assembly programme? On the other mitt, how could the proposed change increment the size of an MIPS associates plan? Expert Answer schajacob answered this 710 answers | 3 | | Was this answer helpful? 2 Definition of MIPS The number of MIPS (meg instructions per second) is a general mensurate of calculating performance and, by implication, the amount of piece of work a larger reckoner can do. For large servers or mainframes, MI PS is a way to measure the cost of calculating: the more MIPS delivered for the coin, the amend the value. Assume that we would like to expand the MIPS register file to 128 registers and expand the instruction gear up to comprise four times as many instructions: The entire MIPS compages is basedl around the fact that instructions are easy to decode and each instruction takes exactly 1 32-chip machine word, which considerably simplifies lots of things: you ever jump a multiple of 4 bytes, you ahways get to fit a round number of nstructions on a cache line, etc. To have 38-striking instructionswould pntirely ruin the elegant MIPS The compromise chosen by the MIPS designers is to go along all instructions the same length, thereby requiring dissimilar kinds of teaching formats for different kinds of instructions. For example, the format in a higher place is chosen R-blazon (for register) or R-format. A 2nd type of education format is called I-type (for immediate) or l-format and is used by the immediate and data transfer instructions. The fields of I-format Here is the meaning of each name of the fields in MIPS instructions: op: Easic functioning of the instruction, traditionally called the opcode. rs: The kickoff register source operand. rt: The second annals source operand. rd: The register destination operand. It gets the result of the operation. shamt: Shift amount, it volition non be used until and then, and hence the field contains zero in this section. funct: Function. This field, often chosen the function code, selects the specific variant of the operation in the op field 1. How this would bear on the size of each of the bit fields in the R-type instructions: 128 Registers,38 bits for each. Annals bits: log2/128) opcodel6rrd shamt functie R-tyoe instructions use the opcode 0 and the funct to denote the operation. Using an unused opcode (there are many) and the same funct combinations, all instructions with base of operations addressing tin can exist added. The length of the firsthand was unspecified . . 16 is a practiced choice since it is a half word, and the size used in -blazon instructions. However, no instruction that uses the shamt field can take base of operations addressing as asked in the question, and so information technology is possible to use the shamt field and allow only 5-bit offsets and retain the instruction ength. 2. How this would affect the size of each of the scrap flelds in the l-type instructions: 128 Registers 36 bits. Register bits: log2 (128)-7 opcode (,) | rs (7) | rt (7 | immediate(16) 2 acceptable answers: 1. No change using the supposition that the definition of an immediate must be an integer constan 2. 37 $.25 for an instruction of the form addi Sa0. Ss1,0St1). We will need to add another 5 bits to incorporate the register data. opcode rsrt mmediate 215) 3.How could each of the two proposed changes subtract the size of an MIPS associates program: 126 Registers Longer instruction-encoding ways longer programs that practice the same operations. The instruction formats may be fifty-fifty larger than indicated higher up since the increases aren't byte-aligned and addressing subsequent instructions is difficult. It also breaks the MIPS tenet of fixad-length instructions. Programs may decrease in size because more registers means you lot tin can 'hold onto more data in the processor without going aut to memory, leading to fower load/shop instructions If the sharnt field is used, the programme volition not abound larger with this addition, though it may abound smaller Howaver, adcing hase-addressing still adds complexity to the processor that may tiresome the program down. It is as well less useful with merely five-bit offsets Evidence transcribed image text

Proficient Answer

. . .

- Description

Source: https://www.courseunlock.org/product/solved-assume-would-like-expand-mips-register-file-128-registers-expand-instruction-set-contain-f-q26491376/

Posted by: briggspretrusiona.blogspot.com

0 Response to "How Could Each Of The Two Proposed Changes Decrease The Size Of An Mips Assemply Program"

Post a Comment